Antenna and RF component design

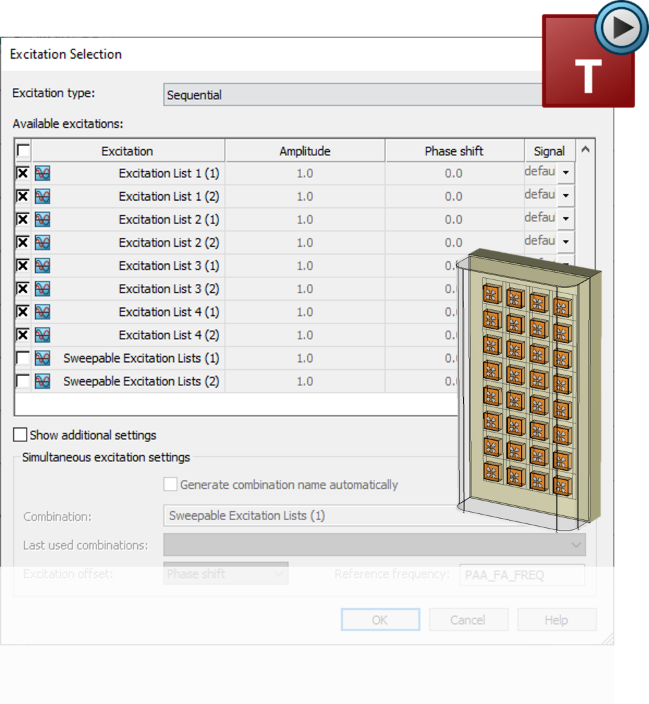

- Sequentially executed excitation lists: The T-solver now enables the sequential excitation of multiple simultaneous excitation lists, enhancing automation in array workflows and making it suitable for Distributed Computing applications.

Note that Sweepable Excitation Lists are still available for a Parameter

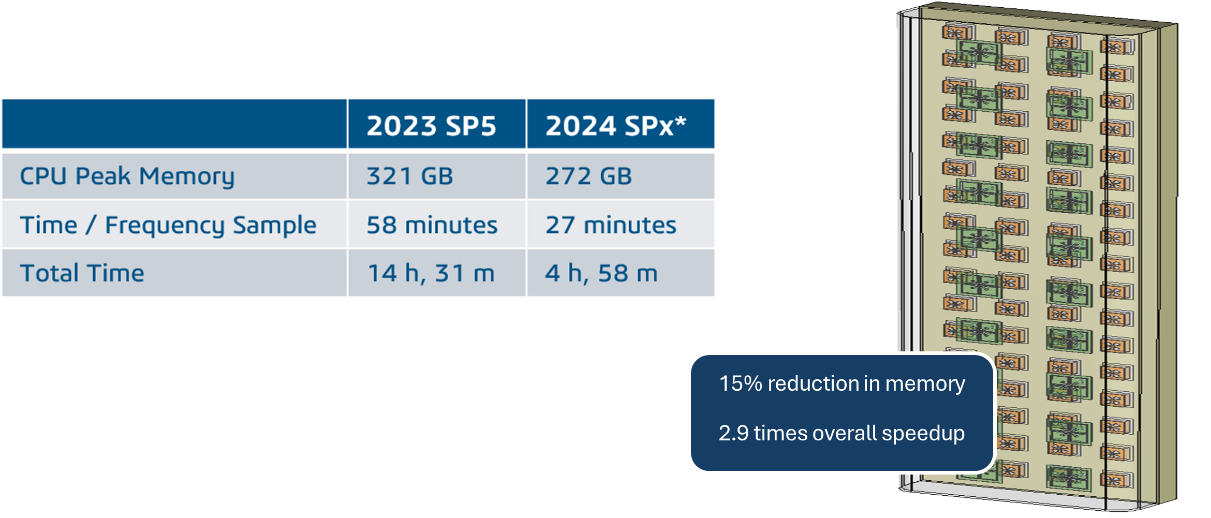

- Key improvements to the Domain Decomposition Solver for Antenna Arrays include(DDM)

- Scalability: load balance of available cores

- MPI: stability and scalability

- Robustness: very high success rate

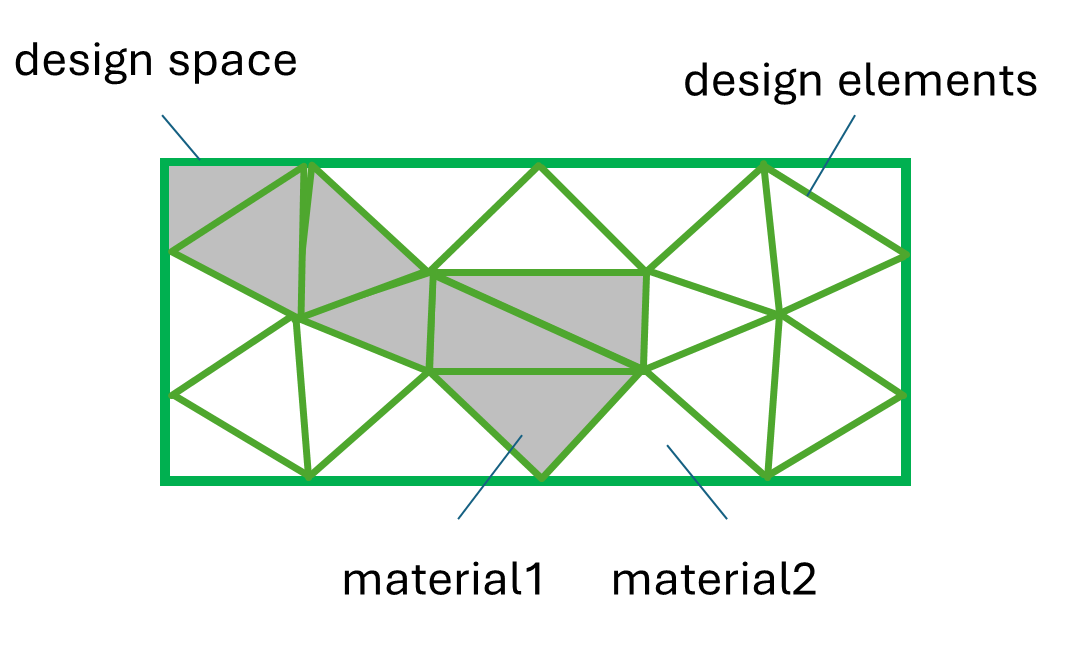

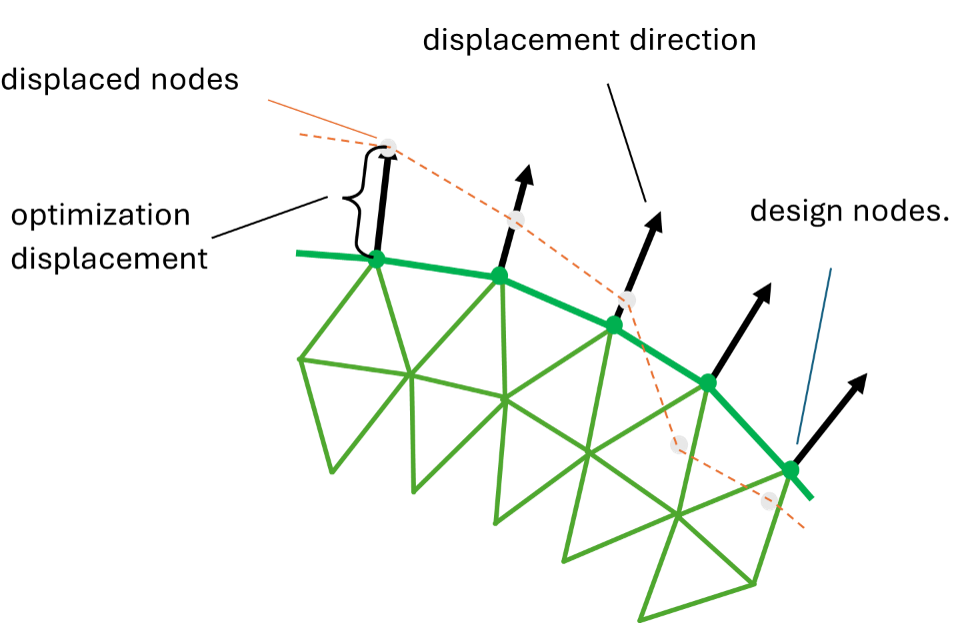

- Enhancements for non-parametric optimization strategies

- Topology Optimization: The purpose is to find function.

- The design space can be a sheet or a volume.

- After optimization the mesh elements will consist of either the original material or the material specified for filling.

- Shape Optimization: The purpose is to achieve high performance.

- The design space must be a surface area.

- After optimization the mesh nodes on the design space will be moved to form a new shape.

Electronics / EDA:

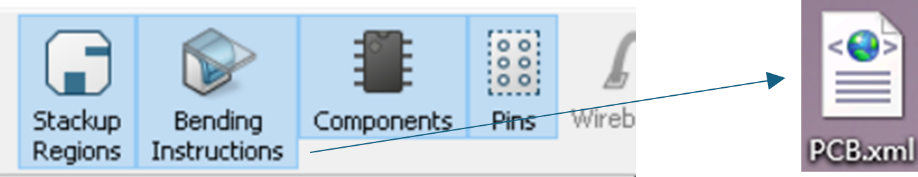

- PCB Import:

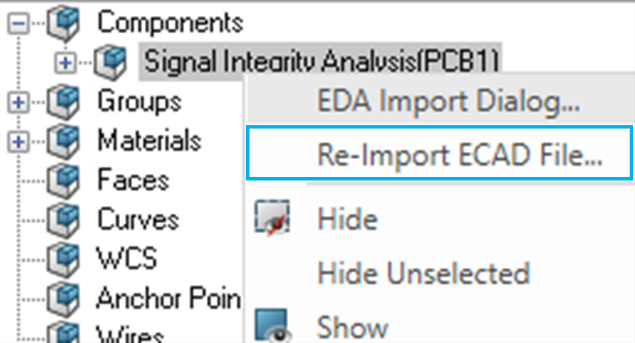

- Reimport PCB: the user can reimport a similar PCB while keeping all the simulation setup

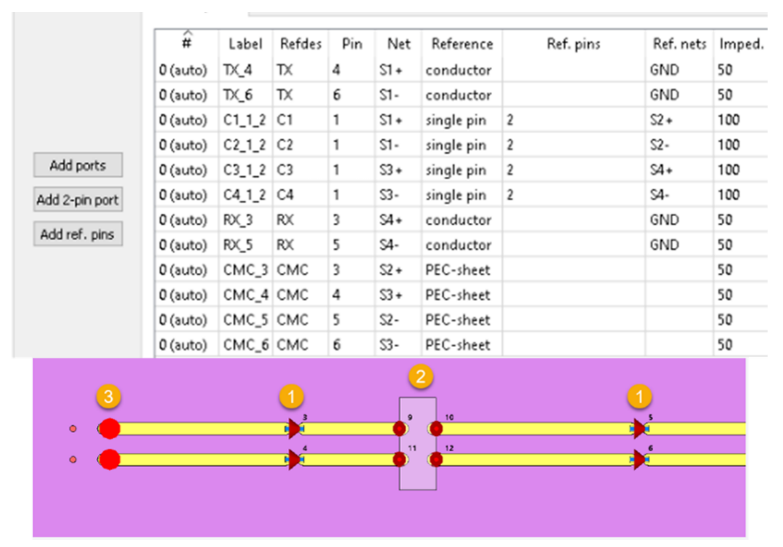

- Port type per component: the user can define different types of port for individual components now both in GUI and python.

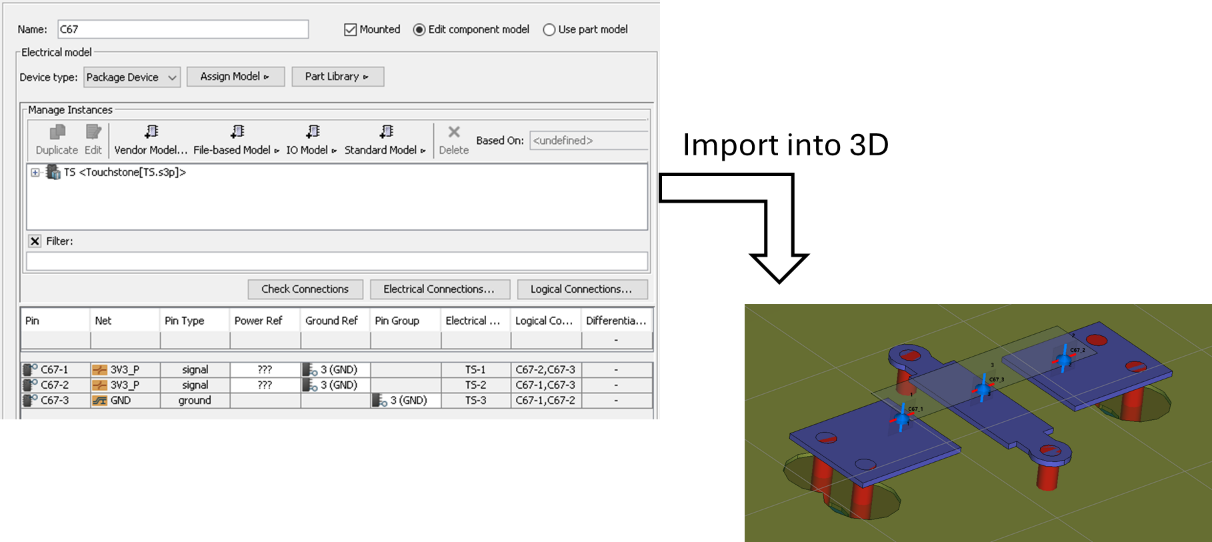

- Multi-pin lumped element: the multi-pin lumped element with TS and SPICE vendor models can be imported into 3D directly.

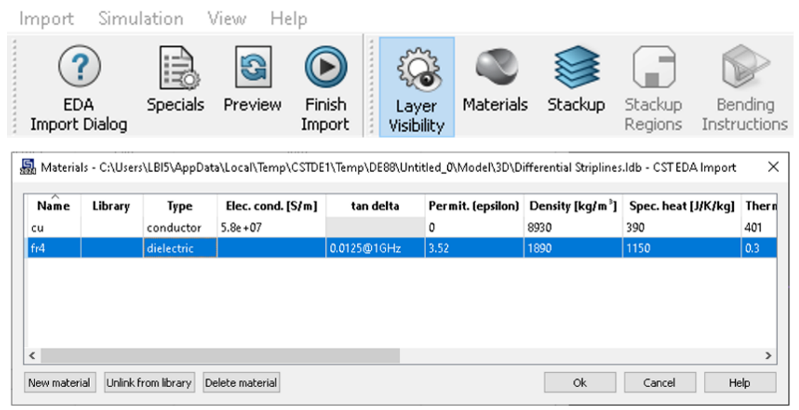

- Material definition: othe users can define new materials and apply to PCB in EDA import dialog.

- Layout Version Schematic (LVS): In the EDA import dialog, we have the capability to verify the logical connection of pins against their physical connection. Upon selecting Preview, an “x” will be shown in the LVS column if there are violations, indicating either all pins of a net being connected or no pins of different nets being connected.

- IPC-2581—C bending and stack up region: supports IPC-2581-C including stackup regions and bending.

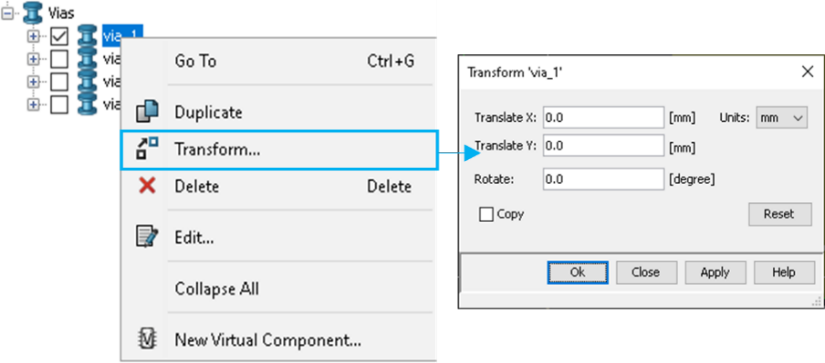

- Transform PCB attributes: This feature is useful when the user would like to modify an imported PCB or create a new PCB in PCBS.

SIGNAL INTEGRITY:

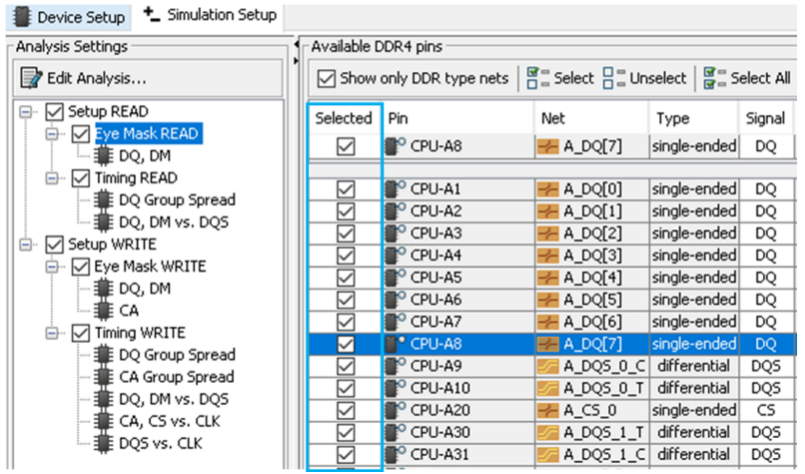

- DDR4 Net Selection: users can run DDR4 analysis for selected nets without manual work or workaround.

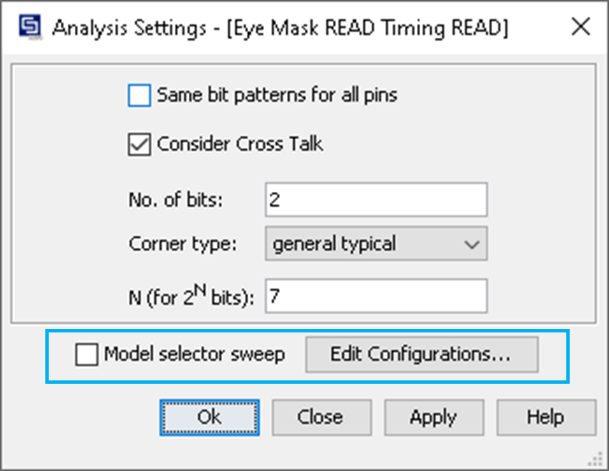

- DDR4 ODT Sweep: users can run model selector sweep in DDR4 Analysis.

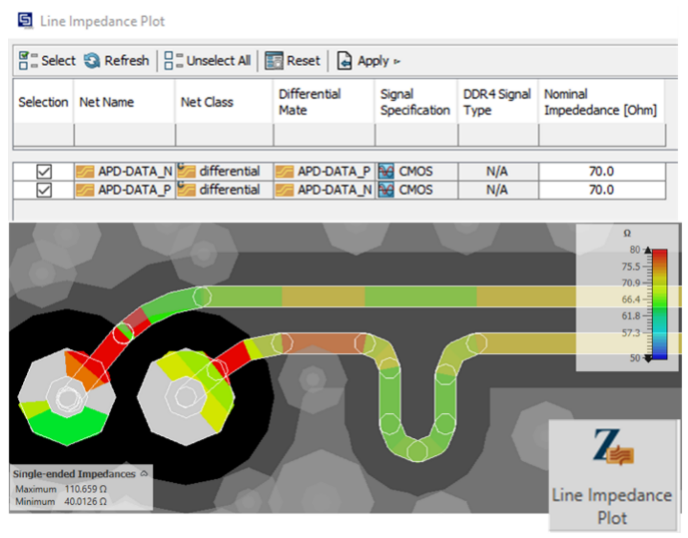

- Line impedance plot: Users can plot the line impedance on the geometry to see any impedance problems that need to be addressed.

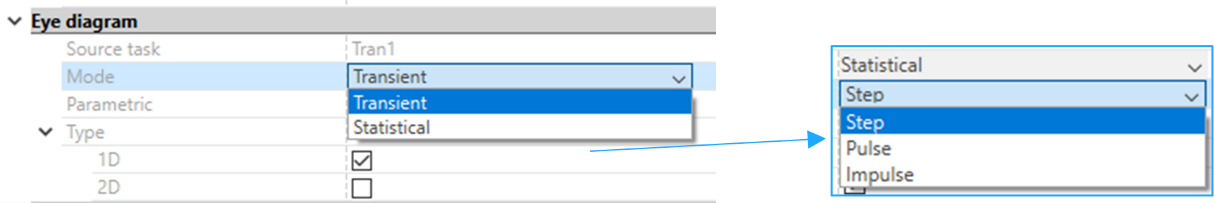

- Statistical 2D Eye Diagram in EAT:

- Eye diagrams are generated in two ways:

- Wrapping waveforms

- Direct from system response (i.e., step response)

- CST Version 2023 eye analysis task (EAT) supports only the transient mode for eye diagram generation by wrapping waveforms. V2024 will support both methods, transient and IBIS-AMI tasks. Users can select step, pulse, or impulse for the system response.

POWER INTEGRITY:

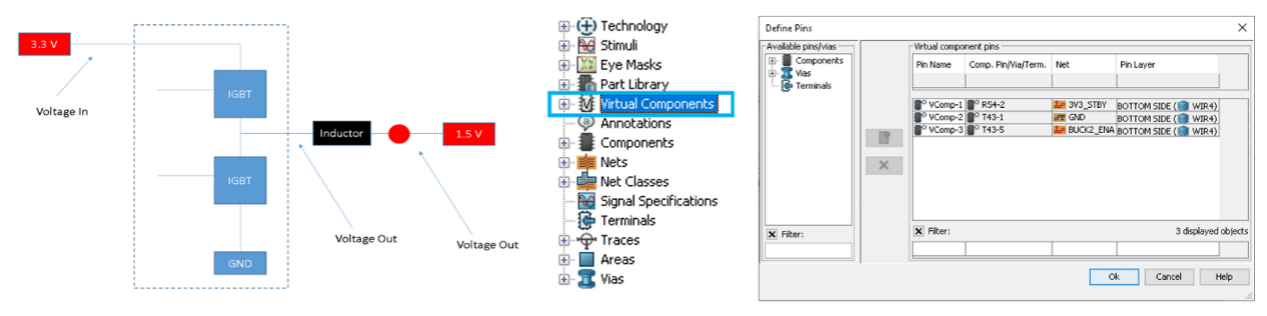

- Virtual Component: oIn the past, users were unable to create a voltage regulator for a DC-DC converter to use in an IR-Drop simulation. V2024 changes this. A virtual component will be defined and used for the voltage regulator.

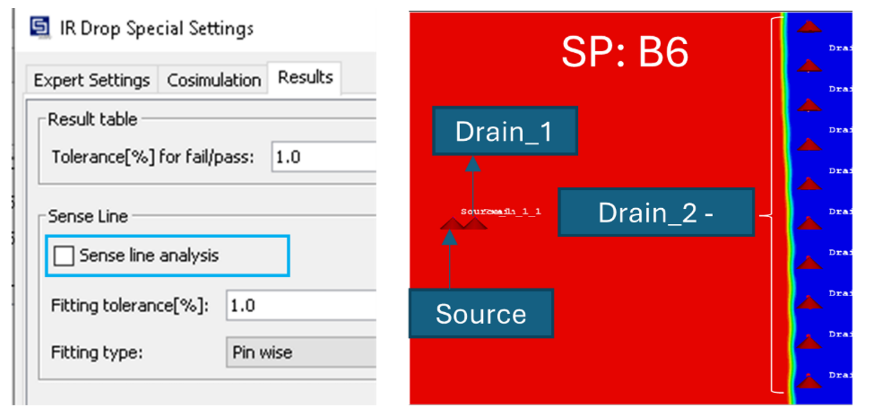

- Sense location analysis: Power supplies typically feature a sense pin that provides voltage feedback from a specific point on the PCB. When dealing with more than two power consumers, determining the optimal location for this sense pin becomes crucial. V2024 offers an analysis tool specifically designed for this purpose. By utilizing the IR-Drop solver, users can conduct a sense line analysis to pinpoint the ideal location for the sense pin.

MULTIPHYSICS SIMULATION:

- 2D Planar loss import: All thermal solvers will now accommodate losses generated from simulations using a 2D planar mesh. Users can now perform motor thermal simulation.

- Dynamic fan speed: Fan can adjust its speed based on temperature readings at a monitor point.

- Solar radiation: Solar radiation feature in V2024 release helps calculating the thermal impact of solar radiation on the system.

ELECTROMAGNETIC COMPATIBILITY:

- Improved sampling

- New S-Parameter sampling scheme for the FD solver (lin-log).

- No re-sampling of S-Parameters when used for Vector Fitting in DES.

- Time gating + Hamming window on by default for periodic signals.

- Field probes after combining results use sampling defined in DES

- Automatic Sampling for Transient Task FFT.

- New Signal Definitions

- All time signal definitions for transient tasks have been reworked.

- Improved usability of spread spectrum definition.

CABLE SIMULATION:

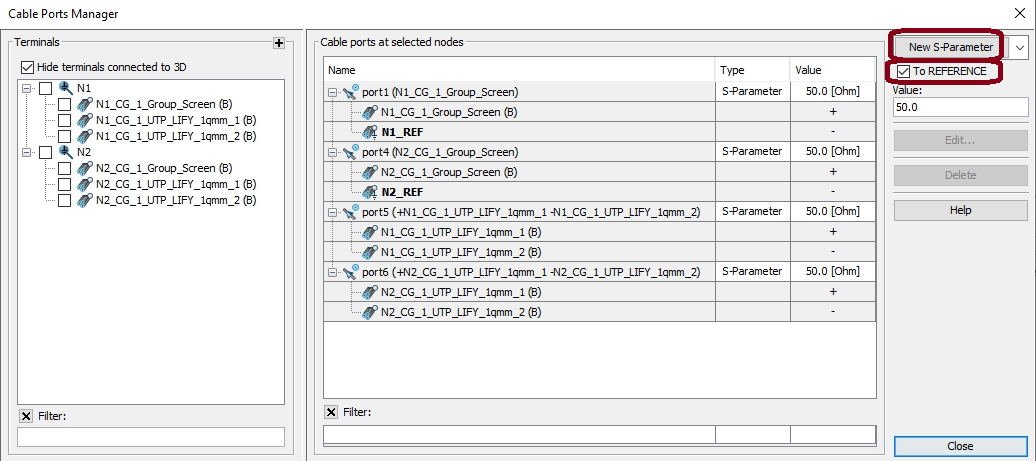

- GUI enhancements:

- Multi-editing allows changing the impedance value of several ports.

- New port button clearly distinguishes between the creation of single-ended ports and differential ports.

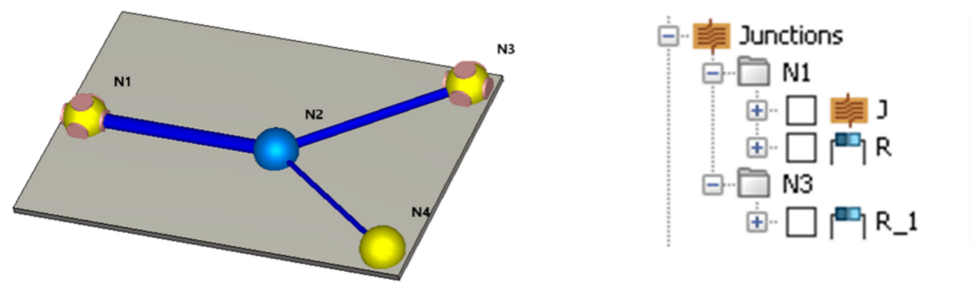

- Cable Junctions are needed to define the loadings on the cable endings.

- Now, these junctions have a representation in the Navigation tree and in the 3D view. This makes it much easier for users to define the simulation setup.

- Cable simulation with ports: Cable ports instead of pins

- Reduce the number of pins of the schematic block, no mixing of ports and CS pins.

- Can run without a schematic setup. Cable port results and current monitor results directly in the 3D navigation tree.

- Cable and 3D ports can be used for a common S-Parameter simulation.

- Combine results, MPI, DC

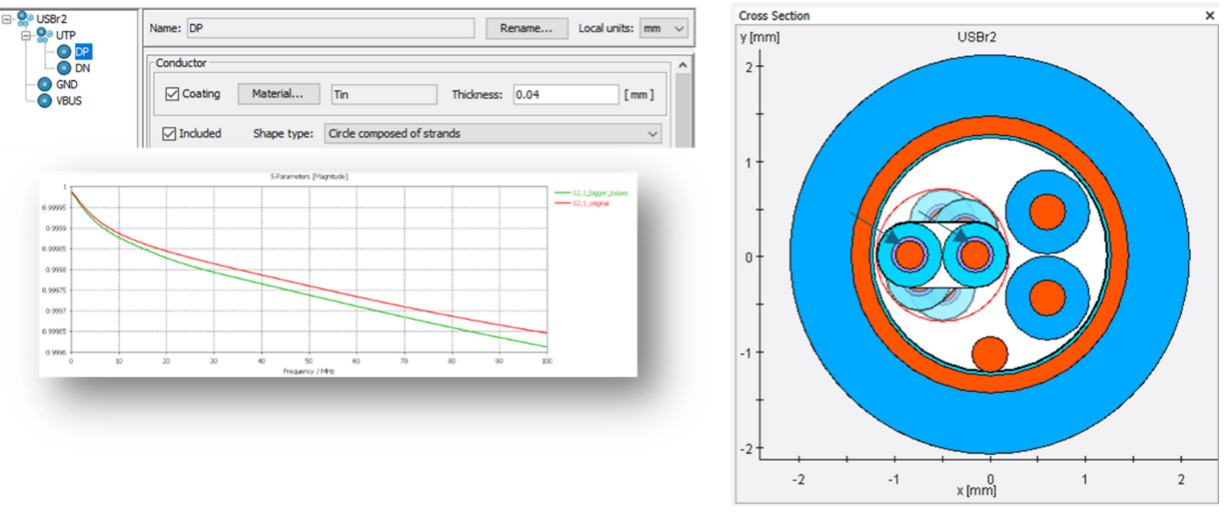

- Support for coated wires:

- For mechanical stability, wires are often coated.

- The coating leads to a changed frequency-dependent conductivity of the wires.

- Single material coating supported in CST Studio Suite 2024

We Urge You To Call Us For Any Doubts & Clarifications That You May Have. We Are Eager to Talk To You

Call Us: +91 7406663589

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

zocHjVxBNP

KhnkETeCrWsiM

Your content consistently impresses me.

pin-up casino giris https://azerbaijancuisine.com/# pin-up

pin-up oyunu

mexican rx online northern doctors reputable mexican pharmacies online

mexico drug stores pharmacies mexican rx online mexican rx online

pharmacies in mexico that ship to usa: mexican pharmacy northern doctors – purple pharmacy mexico price list

buying from online mexican pharmacy: mexican pharmacy northern doctors – medicine in mexico pharmacies

buying prescription drugs in mexico online: mexican pharmacy northern doctors – buying prescription drugs in mexico

mexico pharmacies prescription drugs mexican northern doctors mexican drugstore online

mexican mail order pharmacies: mexican northern doctors – buying prescription drugs in mexico online

https://northern-doctors.org/# medicine in mexico pharmacies

mexican rx online: northern doctors pharmacy – mexican pharmacy

medication from mexico pharmacy: mexican northern doctors – buying from online mexican pharmacy

https://northern-doctors.org/# purple pharmacy mexico price list

buying from online mexican pharmacy: mexican northern doctors – mexico pharmacies prescription drugs

http://northern-doctors.org/# mexico pharmacies prescription drugs

mexico drug stores pharmacies: northern doctors pharmacy – buying prescription drugs in mexico

п»їbest mexican online pharmacies: mexican pharmacy online – medication from mexico pharmacy

mexican border pharmacies shipping to usa mexican pharmacy mexican pharmaceuticals online

http://northern-doctors.org/# buying from online mexican pharmacy

mexico drug stores pharmacies: mexican pharmacy online – п»їbest mexican online pharmacies

mexican online pharmacies prescription drugs: northern doctors pharmacy – medicine in mexico pharmacies

https://northern-doctors.org/# best online pharmacies in mexico

medication from mexico pharmacy: mexican northern doctors – mexican mail order pharmacies

https://northern-doctors.org/# mexican rx online

п»їbest mexican online pharmacies: mexican pharmacy online – purple pharmacy mexico price list

medication from mexico pharmacy: mexican northern doctors – п»їbest mexican online pharmacies

https://northern-doctors.org/# mexican online pharmacies prescription drugs

buying prescription drugs in mexico online mexican mail order pharmacies mexico pharmacies prescription drugs

medication from mexico pharmacy: Mexico pharmacy that ship to usa – п»їbest mexican online pharmacies

http://northern-doctors.org/# mexican rx online

mexican border pharmacies shipping to usa: northern doctors – medication from mexico pharmacy

mexico drug stores pharmacies: mexican pharmacy online – mexico pharmacy

http://northern-doctors.org/# mexican online pharmacies prescription drugs

mexican rx online: reputable mexican pharmacies online – mexican pharmaceuticals online

mexican border pharmacies shipping to usa: mexican northern doctors – mexican border pharmacies shipping to usa

http://northern-doctors.org/# best online pharmacies in mexico

https://cmqpharma.online/# mexican online pharmacies prescription drugs

medicine in mexico pharmacies

medicine in mexico pharmacies

https://cmqpharma.com/# mexican pharmaceuticals online

buying prescription drugs in mexico

mexican mail order pharmacies cmq pharma mexican pharmacy reputable mexican pharmacies online

mexico pharmacies prescription drugs: medicine in mexico pharmacies – buying prescription drugs in mexico online

mexico drug stores pharmacies cmq pharma п»їbest mexican online pharmacies

best online pharmacies in mexico mexican pharmacy online mexican mail order pharmacies

п»їbest mexican online pharmacies cmq mexican pharmacy online mexico drug stores pharmacies

mexican mail order pharmacies online mexican pharmacy п»їbest mexican online pharmacies

buying from online mexican pharmacy mexican online pharmacy mexican mail order pharmacies

mexican mail order pharmacies mexican pharmacy mexican mail order pharmacies

mexican pharmacy mexican pharmacy п»їbest mexican online pharmacies

buying from online mexican pharmacy cmq pharma mexican pharmacy mexican online pharmacies prescription drugs

Online medicine order indian pharmacies safe indian pharmacy online

http://indiapharmast.com/# top online pharmacy india

77 canadian pharmacy canadian pharmacies comparison canadian valley pharmacy

https://indiapharmast.com/# reputable indian online pharmacy

п»їlegitimate online pharmacies india reputable indian online pharmacy india pharmacy mail order

canadian pharmacy com canadian pharmacy 24h com safe canadapharmacyonline

http://foruspharma.com/# buying from online mexican pharmacy

buy amoxicillin online with paypal: amoxicillin no prescipion – how to get amoxicillin

buy amoxicillin online with paypal: amoxicillin online without prescription – amoxicillin cost australia

buy cipro online usa: ciprofloxacin 500mg buy online – ciprofloxacin 500 mg tablet price

doxycycline 100mg coupon: buy doxycycline 100mg capsule – doxycycline cream over the counter

Paxlovid buy online: paxlovid india – paxlovid price

buy doxycycline mexico: doxycycline 50 mg india – purchase doxycycline 100mg

ciprofloxacin 500 mg tablet price: ciprofloxacin generic price – cipro

amoxicillin capsules 250mg: amoxicillin discount coupon – buying amoxicillin online

mexico drug stores pharmacies mexican drugstore online reputable mexican pharmacies online

https://mexicandeliverypharma.online/# buying from online mexican pharmacy

medication from mexico pharmacy: mexican border pharmacies shipping to usa – reputable mexican pharmacies online

mexican online pharmacies prescription drugs: п»їbest mexican online pharmacies – pharmacies in mexico that ship to usa

п»їbest mexican online pharmacies purple pharmacy mexico price list mexican border pharmacies shipping to usa

medication from mexico pharmacy: mexican border pharmacies shipping to usa – best online pharmacies in mexico

buying prescription drugs in mexico online: mexico pharmacies prescription drugs – п»їbest mexican online pharmacies

https://mexicandeliverypharma.online/# mexican mail order pharmacies

mexican pharmacy mexican online pharmacies prescription drugs п»їbest mexican online pharmacies

medication from mexico pharmacy: mexican online pharmacies prescription drugs – buying from online mexican pharmacy

mexican pharmaceuticals online: medicine in mexico pharmacies – mexican border pharmacies shipping to usa

https://mexicandeliverypharma.com/# mexican drugstore online

mexico pharmacies prescription drugs: mexico drug stores pharmacies – mexican drugstore online

medicine in mexico pharmacies mexican border pharmacies shipping to usa purple pharmacy mexico price list

reputable mexican pharmacies online: buying from online mexican pharmacy – mexican drugstore online

mexican pharmaceuticals online: purple pharmacy mexico price list – purple pharmacy mexico price list

п»їbest mexican online pharmacies: medicine in mexico pharmacies – mexico drug stores pharmacies

mexican drugstore online mexico drug stores pharmacies buying prescription drugs in mexico online

mexico drug stores pharmacies: buying prescription drugs in mexico online – mexican drugstore online

mexican mail order pharmacies: mexican drugstore online – medication from mexico pharmacy

mexican mail order pharmacies: п»їbest mexican online pharmacies – best online pharmacies in mexico

mexican online pharmacies prescription drugs mexico drug stores pharmacies best online pharmacies in mexico

buying prescription drugs in mexico online: mexico drug stores pharmacies – mexican border pharmacies shipping to usa

purple pharmacy mexico price list: mexican mail order pharmacies – buying from online mexican pharmacy

mexico drug stores pharmacies: buying prescription drugs in mexico online – mexican rx online

mexico drug stores pharmacies mexican rx online mexican pharmacy

mexican online pharmacies prescription drugs: pharmacies in mexico that ship to usa – pharmacies in mexico that ship to usa

pharmacies in mexico that ship to usa: mexican drugstore online – buying prescription drugs in mexico online

mexico drug stores pharmacies: purple pharmacy mexico price list – mexican border pharmacies shipping to usa

mexican rx online reputable mexican pharmacies online mexican drugstore online

purple pharmacy mexico price list: mexican online pharmacies prescription drugs – reputable mexican pharmacies online

mexico pharmacies prescription drugs: reputable mexican pharmacies online – mexican drugstore online

mexican mail order pharmacies: pharmacies in mexico that ship to usa – mexican mail order pharmacies

mexican mail order pharmacies reputable mexican pharmacies online mexican pharmaceuticals online

medicine in mexico pharmacies: mexican mail order pharmacies – reputable mexican pharmacies online

mexican online pharmacies prescription drugs: medicine in mexico pharmacies – buying prescription drugs in mexico

mexican border pharmacies shipping to usa: mexican mail order pharmacies – mexican rx online

purple pharmacy mexico price list п»їbest mexican online pharmacies buying from online mexican pharmacy

mexican mail order pharmacies: mexican drugstore online – buying prescription drugs in mexico online

medicine in mexico pharmacies: best online pharmacies in mexico – best online pharmacies in mexico

mexican mail order pharmacies: mexican drugstore online – medicine in mexico pharmacies

medicine in mexico pharmacies mexico drug stores pharmacies mexican drugstore online

mexican drugstore online: buying prescription drugs in mexico online – mexican border pharmacies shipping to usa

purple pharmacy mexico price list: reputable mexican pharmacies online – buying prescription drugs in mexico

buying from online mexican pharmacy: п»їbest mexican online pharmacies – mexican drugstore online

mexican pharmacy buying prescription drugs in mexico online mexican online pharmacies prescription drugs

mexican mail order pharmacies: reputable mexican pharmacies online – buying prescription drugs in mexico

mexico drug stores pharmacies: pharmacies in mexico that ship to usa – mexican mail order pharmacies

mexico pharmacy medication from mexico pharmacy mexican rx online

mexican border pharmacies shipping to usa: medication from mexico pharmacy – buying from online mexican pharmacy

buying prescription drugs in mexico: pharmacies in mexico that ship to usa – purple pharmacy mexico price list

pharmacies in mexico that ship to usa: mexican rx online – medication from mexico pharmacy

buying prescription drugs in mexico mexican rx online mexican mail order pharmacies

mexico drug stores pharmacies: medication from mexico pharmacy – buying from online mexican pharmacy

mexican pharmaceuticals online: purple pharmacy mexico price list – mexico drug stores pharmacies

mexico drug stores pharmacies: purple pharmacy mexico price list – mexican pharmaceuticals online

best online pharmacies in mexico reputable mexican pharmacies online п»їbest mexican online pharmacies

pharmacies in mexico that ship to usa: mexico drug stores pharmacies – mexico pharmacies prescription drugs

buying from online mexican pharmacy: mexico pharmacies prescription drugs – best online pharmacies in mexico

best online pharmacies in mexico: buying prescription drugs in mexico online – mexican online pharmacies prescription drugs

purple pharmacy mexico price list buying prescription drugs in mexico mexican border pharmacies shipping to usa

mexico pharmacies prescription drugs: buying prescription drugs in mexico – best online pharmacies in mexico

medicine in mexico pharmacies: п»їbest mexican online pharmacies – п»їbest mexican online pharmacies

buying prescription drugs in mexico: mexican online pharmacies prescription drugs – mexican drugstore online

purple pharmacy mexico price list mexican border pharmacies shipping to usa mexican mail order pharmacies

medication from mexico pharmacy: mexican rx online – medication from mexico pharmacy

buying prescription drugs in mexico: mexican mail order pharmacies – mexican rx online

mexican mail order pharmacies: medicine in mexico pharmacies – mexican online pharmacies prescription drugs

mexican border pharmacies shipping to usa buying from online mexican pharmacy medication from mexico pharmacy

mexican online pharmacies prescription drugs: mexico drug stores pharmacies – medication from mexico pharmacy

mexican border pharmacies shipping to usa: pharmacies in mexico that ship to usa – mexican online pharmacies prescription drugs

reputable mexican pharmacies online: mexican drugstore online – buying prescription drugs in mexico

order cheap propecia prices get generic propecia without dr prescription order cheap propecia no prescription

tamoxifen vs raloxifene: low dose tamoxifen – tamoxifen effectiveness

http://nolvadexbestprice.pro/# nolvadex 20mg

http://cytotecbestprice.pro/# buy cytotec pills online cheap

tamoxifen citrate pct raloxifene vs tamoxifen nolvadex for pct

arimidex vs tamoxifen bodybuilding: nolvadex half life – tamoxifen hot flashes

http://cytotecbestprice.pro/# Misoprostol 200 mg buy online

http://zithromaxbestprice.pro/# zithromax drug

Abortion pills online buy cytotec online fast delivery buy cytotec online

buy cytotec over the counter: buy misoprostol over the counter – buy cytotec

http://prednisonebestprice.pro/# prednisone 5 mg

http://nolvadexbestprice.pro/# tamoxifen medication

cost of cheap propecia online get generic propecia online cost propecia tablets

order generic propecia: buy propecia without rx – cost generic propecia pill

buy cytotec over the counter: cytotec abortion pill – buy misoprostol over the counter

tamoxifen chemo: nolvadex price – tamoxifen bone pain

http://nolvadexbestprice.pro/# common side effects of tamoxifen

tamoxifen alternatives premenopausal: tamoxifen joint pain – tamoxifen skin changes

propecia generic: cheap propecia prices – cost cheap propecia without dr prescription

Abortion pills online: buy cytotec over the counter – purchase cytotec

https://nolvadexbestprice.pro/# where can i buy nolvadex

raloxifene vs tamoxifen: tamoxifen benefits – nolvadex pills

tamoxifen benefits: tamoxifen dose – tamoxifenworld

farmacia online: Cialis generico 20 mg 8 compresse prezzo – comprare farmaci online con ricetta

acquisto farmaci con ricetta: farmaci senza ricetta elenco – farmacia online piГ№ conveniente

top farmacia online: kamagra gold – comprare farmaci online con ricetta

acquistare farmaci senza ricetta: Cialis generico farmacia – Farmacie online sicure

https://cialisgenerico.life/# farmacie online sicure

comprare farmaci online all’estero: sildenafil oral jelly 100mg kamagra – farmacia online

acquisto farmaci con ricetta: kamagra oral jelly – Farmacie on line spedizione gratuita

Farmacie online sicure: kamagra gold – farmacia online senza ricetta

comprare farmaci online con ricetta: Farmacia online piu conveniente – acquistare farmaci senza ricetta

https://kamagrait.pro/# comprare farmaci online all’estero

viagra generico prezzo piГ№ basso: acquisto viagra – viagra naturale

viagra pfizer 25mg prezzo: viagra senza prescrizione – kamagra senza ricetta in farmacia

migliori farmacie online 2024: Cialis generico 20 mg 8 compresse prezzo – Farmacie on line spedizione gratuita

http://cialisgenerico.life/# farmacia online piГ№ conveniente

https://sildenafil.llc/# viagra dosage

where to buy cialis online: cialis without a doctor prescription – trial pack cialis viagra levitro

generic viagra available: buy sildenafil online usa – generic viagra overnight

http://sildenafil.llc/# buy viagra online without a prescription

cialis 20mg prices: cialisВ® – cipla cialis

For anyone who hopes to find valuable information on that topic, right here is the perfect blog I would highly recommend. Feel free to visit my site QH9 for additional resources about Airport Transfer.

viagra vs cialis: buy sildenafil online usa – viagra prices

https://tadalafil.auction/# cialis black 800mg

http://edpillpharmacy.store/# online ed prescription

get ed meds online: online ed prescription same-day – ed rx online

http://indiapharmacy.shop/# reputable indian pharmacies

ed treatment online

http://indiapharmacy.shop/# indian pharmacy

cheap ed medication

mexico pharmacies prescription drugs: Certified Mexican pharmacy – mexico drug stores pharmacies

http://edpillpharmacy.store/# ed med online

http://indiapharmacy.shop/# top 10 pharmacies in india

best online ed pills

cheapest ed online: ed medicines online – best ed pills online

http://edpillpharmacy.store/# online ed treatments

low cost ed meds online: Best ED pills non prescription – ed doctor online

pills for ed online: online ed prescription same-day – ed online treatment

http://edpillpharmacy.store/# cheap ed drugs

mexican pharmaceuticals online: Best pharmacy in Mexico – best online pharmacies in mexico

http://mexicopharmacy.win/# purple pharmacy mexico price list

reputable indian online pharmacy: Online medicine order – indian pharmacies safe

https://edpillpharmacy.store/# ed medications online

mexico drug stores pharmacies: Purple pharmacy online ordering – mexican mail order pharmacies

Online medicine order: indian pharmacy – indian pharmacies safe

https://mexicopharmacy.win/# buying from online mexican pharmacy

medication from mexico pharmacy: mexican pharmacy – medication from mexico pharmacy

https://indiapharmacy.shop/# india online pharmacy

pharmacies in mexico that ship to usa: Medicines Mexico – pharmacies in mexico that ship to usa

reputable indian online pharmacy: Online India pharmacy – top online pharmacy india

http://mexicopharmacy.win/# medication from mexico pharmacy

erectile dysfunction medication online: Cheap ED pills online – ed medication online

https://mexicopharmacy.win/# mexican border pharmacies shipping to usa

mexico drug stores pharmacies: mexico pharmacy win – mexico pharmacies prescription drugs

order ed pills: online ed prescription same-day – online ed meds

Online medicine order: Online medicine home delivery – indian pharmacy paypal

buying prescription drugs in mexico: Certified Mexican pharmacy – medicine in mexico pharmacies

top 10 pharmacies in india: Indian pharmacy online – indian pharmacy paypal

https://lipitor.guru/# generic lipitor

20 mg lisinopril without a prescription: cheap lisinopril – lisinopril 10 mg brand name in india

buy cytotec pills https://tamoxifen.bid/# tamoxifenworld

lasix for sale

nolvadex pct: tamoxifen adverse effects – tamoxifen joint pain

It’s easy to see why: the game is simple and easy to learn, yet challenging and addictive. There are millions of 8 Ball Pool players around the world, and the game is played in countries all over the world. The first player to pocket all of their balls, wins the game. Mahjong is a traditional game established in China about 100 years ago. Classic mahjong was played with 144 mahjong tiles and four players. It is a social game that allows friends and family to get together and have fun. The online mahjong rules are simple — match identical mahjong tiles that are not covered, and free from sides. Any special tiles such as flower tiles and season tiles can be matched. You can learn more about scoring and how to play mahjong by clicking the question mark in the upper-right corner of the mahjong games. You will want to challenge yourself by matching the tiles quickly because the game is timed. Best of all: You can play mahjong online — no download needed!

https://yenkee-wiki.win/index.php?title=All_slots_welcome_bonus

Video poker games aren’t as simple as slots so you would need to choose the perfect poker machine for your play. In this article, we will guide you on how to select the best video poker machine. Video poker is an easy game to learn, but a difficult one to master. Moving from video poker beginner to an advanced player means knowing your video poker terminology. If you learn some of the most common terms before you play video poker, you’ll increase your chances of reacting to game cues in good time from the start. Free video poker offers all the fun, exciting gameplay you’d expect from a real money version If applied equally to video poker and slots, those multi-point days sometimes could turn some video poker games profitable for players, but can’t do the same on the slots. For many years, video poker zeroed in on multiple-points days to gain an advantage.

Misoprostol 200 mg buy online https://lipitor.guru/# lipitor 10 mg tablet

furosemide 100mg

http://lisinopril.guru/# lisinopril 250mg

cost of lisinopril 40mg cheap lisinopril cost of lisinopril 30 mg

buy cytotec in usa: buy cytotec online – Cytotec 200mcg price

cytotec pills buy online https://tamoxifen.bid/# generic tamoxifen

lasix medication

http://lisinopril.guru/# lisinopril 2

buy cytotec pills https://lipitor.guru/# lipitor 80

lasix medication

over the counter lisinopril lisinopril capsule lisinopril 5 mg buy

buy cytotec online: purchase cytotec – Cytotec 200mcg price

https://cytotec.pro/# Cytotec 200mcg price

furosemide 100mg: buy furosemide – furosemida

Misoprostol 200 mg buy online https://lisinopril.guru/# buy lisinopril 20 mg without prescription

buy lasix online

https://lipitor.guru/# lipitor otc

Abortion pills online: buy misoprostol tablet – cytotec pills buy online

buy cytotec http://cytotec.pro/# buy cytotec online fast delivery

furosemide 100 mg

liquid tamoxifen: buy tamoxifen online – alternative to tamoxifen

http://cytotec.pro/# Cytotec 200mcg price

buy cytotec pills online cheap: cheapest cytotec – buy cytotec pills online cheap

buy cytotec https://tamoxifen.bid/# nolvadex pct

furosemide 40mg

buy cytotec in usa: cytotec online – buy cytotec online fast delivery

lisinopril 2.5 pill: price lisinopril 20 mg – buy lisinopril 5mg

Cytotec 200mcg price https://tamoxifen.bid/# tamoxifen therapy

furosemide

п»їcytotec pills online: cheapest cytotec – cytotec abortion pill

lasix 40 mg: furosemide online – lasix generic name

buy cytotec online https://lipitor.guru/# lipitor 10 mg cost

buy furosemide online

lipitor lowest price: Lipitor 10 mg price – buy generic lipitor online

buy cytotec online: cheapest cytotec – Cytotec 200mcg price

cytotec abortion pill http://tamoxifen.bid/# tamoxifen buy

lasix for sale

http://easyrxcanada.com/# pharmacy wholesalers canada

indian pharmacy paypal reputable indian pharmacies online pharmacy india

https://easyrxcanada.online/# pharmacy in canada

recommended canadian pharmacies legit canadian pharmacy pharmacy wholesalers canada

https://easyrxindia.com/# online shopping pharmacy india

https://easyrxcanada.com/# canadian online pharmacy

cheapest online pharmacy india: indian pharmacies safe – reputable indian pharmacies

cheapest online pharmacy india: indian pharmacy – Online medicine home delivery

canadian pharmacy antibiotics legit canadian pharmacy canadian family pharmacy

https://mexstarpharma.online/# mexican online pharmacies prescription drugs

mexican mail order pharmacies: mexican online pharmacies prescription drugs – mexican online pharmacies prescription drugs

https://easyrxindia.com/# online shopping pharmacy india

top 10 pharmacies in india: buy medicines online in india – indian pharmacy paypal

cheapest online pharmacy india: world pharmacy india – indian pharmacy online

https://easyrxcanada.com/# legit canadian pharmacy

https://mexstarpharma.com/# mexican rx online

indian pharmacy online: indian pharmacy paypal – Online medicine home delivery

canadian pharmacy ratings: my canadian pharmacy – canadian pharmacy ed medications

deneme bonusu: bonus veren siteler – deneme bonusu veren siteler

yasal slot siteleri: slot kumar siteleri – deneme bonusu veren siteler

slot siteleri 2024: slot siteleri guvenilir – en guvenilir slot siteleri

http://denemebonusuverensiteler.win/# bahis siteleri

guncel sweet bonanza: sweet bonanza indir – sweet bonanza indir

slot siteleri: slot oyun siteleri – en iyi slot siteleri 2024

http://slotsiteleri.bid/# deneme bonusu veren siteler

slot siteleri bonus veren: oyun siteleri slot – bonus veren casino slot siteleri

https://denemebonusuverensiteler.win/# bahis siteleri

slot siteleri 2024: canl? slot siteleri – casino slot siteleri

https://slotsiteleri.bid/# en iyi slot siteler

slot oyun siteleri: slot casino siteleri – canl? slot siteleri

https://denemebonusuverensiteler.win/# bonus veren siteler

slot siteleri bonus veren: slot siteleri 2024 – 2024 en iyi slot siteleri

https://vavada.auction/# vavada online casino

пинап казино: pin up – пин ап

пин ап казино вход: пинап казино – pin up казино

I don’t think the title of your article matches the content lol. Just kidding, mainly because I had some doubts after reading the article.

вавада рабочее зеркало: казино вавада – vavada зеркало

pin up казино: пин ап вход – пинап казино

пинап казино pin up казино пин ап вход

https://vavada.auction/# вавада казино

вавада зеркало: vavada казино – вавада зеркало

пинап казино: pin up – pin up казино

I like this blog so much, saved to bookmarks.

http://1win.directory/# 1win зеркало

1xbet: зеркало 1хбет – зеркало 1хбет

https://1win.directory/# 1win

1xbet: 1xbet зеркало – 1xbet официальный сайт мобильная версия

https://1xbet.contact/# 1xbet официальный сайт мобильная версия

orlistat online pharmacy uk: pharmacy intern drug store – legit online pharmacy cialis

https://pharm24on.com/# testosterone online pharmacy

kroger pharmacy lisinopril

https://pharm24on.com/# propranolol uk pharmacy

texas online pharmacy

online pharmacy provigil modafinil: target pharmacy augmentin – cialis in indian pharmacy

https://easydrugrx.com/# my rx pharmacy

flonase pharmacy

asacol online pharmacy: Cytotec – online pharmacy ventolin

wholesale pharmacy: viagra australian pharmacy – online pharmacy ambien

https://pharm24on.com/# pharmacy drug store in finland

russian pharmacy online usa

pharmacy assistant certification online: wellbutrin online pharmacy – publix pharmacy cipro

review online pharmacy: online pharmacy percocet no prescription – global online pharmacy

Are you up to the Challenge? Complete your three daily goals and earn prizes! Zynga Poker attracts a huge player pool of casuals trying their luck at poker. The game initially attracts new players by rewarding them with a substantial bonus for registering an account and checking in for the first time. However, the “freemium” business concept underlies Zynga Poker. In other words, the game itself is free, but you can also purchase extra items inside the app, usually for a cheaper rate, to get better prizes. Texas Hold’em is played with a standard deck of 52 playing cards. Player left of the dealer is called the left blind, also known as the small blind; they make the initial bet in the game. The player left of the left blind is called the right blind, also known as the big blind; they double the bet of the left blind. The positions of the dealer and the two blinds rotate clockwise after each game. The dealer is identified by the small black dealer button with D next to one of the poker players.

https://arthurifzz294062.ivasdesign.com/50765273/article-under-review

Yes, under online gambling laws, Texas residents aged 18 and older can use social casino sites to gamble online. Texas is one of 49 states that permit online social casino play, with Washington State being the only outlier. You cannot currently use an online casino real money Texas site, as the law does not permit it, so social and sweepstakes casinos are the only options right now. With no downloading required, you can now play your favorite slot machine game for free from any device! Simply login with your email address or Facebook account and play! Discover the thrill without the hassle! You no longer have to pay to be entertained! Play for free today to win the ultimate Jackpot! Social and sweepstakes casinos have become a popular option for fans of slots and casino games. That is especially true in states like California that do not allow real money gambling online. By using token systems to power their games, these sites abide by state laws while still allowing players to play various slot titles and in some cases have opportunities to claim cash prizes.

online pharmacy percocet: women’s health – gold pharmacy online

female viagra pharmacy: online discount pharmacy – people pharmacy store

https://pharmbig24.online/# lipitor mail order pharmacy

italian pharmacy online Neurontin online pharmacy price checker

purple pharmacy mexico price list: mexican border pharmacies shipping to usa – mexican border pharmacies shipping to usa

pharmacies in mexico that ship to usa: mexican drugstore online – pharmacies in mexico that ship to usa

india pharmacy mail order: mail order pharmacy india – indian pharmacy paypal

pharmacies in mexico that ship to usa: п»їbest mexican online pharmacies – best online pharmacies in mexico

http://mexicopharmacy.cheap/# mexico drug stores pharmacies

indian pharmacy india pharmacy pharmacy website india

top online pharmacy india: п»їlegitimate online pharmacies india – best online pharmacy india

terbinafine target pharmacy: Prasugrel – legal online pharmacy

mexico drug stores pharmacies mexico pharmacies prescription drugs mexico pharmacies prescription drugs

http://pharmbig24.com/# magellan rx specialty pharmacy

indianpharmacy com: pharmacy website india – indianpharmacy com

buying prescription drugs in mexico: buying from online mexican pharmacy – mexican rx online

reputable mexican pharmacies online buying from online mexican pharmacy purple pharmacy mexico price list

top 10 pharmacies in india: top online pharmacy india – top online pharmacy india

https://mexicopharmacy.cheap/# mexico pharmacies prescription drugs

indianpharmacy com cheapest online pharmacy india reputable indian pharmacies

buying from online mexican pharmacy: buying prescription drugs in mexico online – pharmacies in mexico that ship to usa

Online medicine order: Online medicine home delivery – india pharmacy mail order

http://indianpharmacy.company/# reputable indian online pharmacy

losartan pharmacy rx to go pharmacy league city online pharmacy sumatriptan

purple pharmacy mexico price list: buying from online mexican pharmacy – mexican border pharmacies shipping to usa

venlor xr generic effexor xr pharmacy: provigil overseas pharmacy – target pharmacy meloxicam

online pharmacy no prescription flagyl: buying viagra from pharmacy – rx hmong pharmacy

india pharmacy pharmacy website india buy medicines online in india

Hello, Neat post. There is an issue together with your website in internet explorer, may check thisK IE nonetheless is the marketplace leader and a huge part of folks will miss your wonderful writing because of this problem.

http://pharmbig24.com/# minocycline pharmacy price

mexican mail order pharmacies: mexican pharmaceuticals online – pharmacies in mexico that ship to usa

overnight pharmacy 4u cialis: overseas pharmacy no prescription – rx pharmacy richland washington

india pharmacy india pharmacy mail order Online medicine order

http://mexicopharmacy.cheap/# buying prescription drugs in mexico

india pharmacy mail order: Online medicine home delivery – reputable indian online pharmacy

I am continually searching online for ideas that can facilitate me. Thx!

cialis online pharmacy australia online pharmacy prozac no prescription prescription cost

india online pharmacy: india online pharmacy – world pharmacy india

Well I really enjoyed reading it. This subject offered by you is very effective for good planning.

best online pharmacies in mexico: mexican border pharmacies shipping to usa – medication from mexico pharmacy

value rx pharmacy irvine Nimotop dapoxetine

https://pharmbig24.online/# ketoconazole shampoo pharmacy

online shopping pharmacy india: reputable indian pharmacies – best online pharmacy india

guardian pharmacy viagra: jewel osco pharmacy – friendly rx pharmacy

pharmacy warfarin counseling value rx pharmacy irvine community pharmacy warfarin

http://pharmbig24.com/# humana rx pharmacy

can you buy viagra from pharmacy: best online ambien pharmacy – Levitra Oral Jelly

which pharmacy is cheaper: online pharmacy metronidazole – mtf hormones online pharmacy

india online pharmacy best india pharmacy indian pharmacy paypal

gates of olympus turkce gates of olympus demo turkce oyna gates of olympus oyna demo

http://gatesofolympusoyna.online/# Gates of Olympus

starz bet giris starzbet guvenilir mi starzbet guncel giris

gates of olympus giris gate of olympus oyna gates of olympus turkce

http://starzbet.shop/# starzbet guvenilir mi

http://betine.online/# betine giris

betine giris betine promosyon kodu 2024 betine guncel giris

Thank you for supporting us. We founded this site last year and have been improving it bit by bit everyday. We offer hundreds thousands of free online games in our catalog and add new games daily.You can check out our blog to see what new games we recently added. Do you have game requests? Please comment or leave your feedback here. A little game to create punk songs and watch a band play it for you 🙂 It’s an oldie but a goodie (I hope) Punk-o-matic 2 is in the maki… FreeCell Solitaire, a renowned card game, offers a distinctive twist on traditional solitaire. Unlike its counterparts, it provides players with the opportunity to showcase their strategic prowess. The objective is to move all 52 cards to foundation piles, arranging them in ascending order from Ace to King, following suit. What sets FreeCell apart is the open tableau, where you can strategically maneuver cards to conquer this intricate puzzle. Each move requires thought and foresight, making FreeCell Solitaire a game that combines logic, strategy, and the satisfaction of victory.

https://ejjii.com/list.php?part=2024/08/21/134

Upon reaching Adventure Rank 20, a new event called “People’s Choice” will appear in your event menu. This event also signifies the unlocking of the Spiral Abyss in the Musk Reef, which serves as Genshin Impact’s endgame content—a floor-based dungeon battle. To obtain Xiangling for free, players need to successfully complete Floor 3, Chamber 3 of the Spiral Abyss. Genshin Impact is set to release for PlayStation 4, PC, and mobile devices this year, with a Nintendo Switch version also in the works. Genshin Impact Walkthrough & Guides Wiki Chiori is an Inazuma character but leaks suggest she and her vision is related to Fontaine. She is a fashion designer who designed Navia’s outfit, and maybe Ayaka’s too. She will first appear in the main 4.3 event Roses and Muskets and is rumored to officially be playable in Genshin Impact 4.5. Not much is known about her talents, vision, or weapon type; however, leakers suspect she will be a five-star Geo character.

http://gatesofolympusoyna.online/# gates of olympus oyna demo

casibom giris casibom giris casibom

http://farmaciaeu.com/# farmacia online barata

farmacia online madrid

farmacia online envГo gratis: Tadalafilo precio – farmacia online 24 horas

https://sildenafilo.men/# sildenafilo sandoz 100 mg precio

farmacia online barata y fiable farmacia online 24 horas farmacias online seguras en espaГ±a

farmacia online barata: farmacia online barata y fiable – farmacias direct

http://tadalafilo.bid/# farmacias online seguras en espaГ±a

farmacia gibraltar online viagra: comprar viagra – viagra online cerca de malaga

farmacia online envГo gratis cialis 20 mg precio farmacia farmacias online seguras en espaГ±a

https://farmaciaeu.com/# farmacia online barata y fiable

farmacia barata

https://sildenafilo.men/# sildenafilo 50 mg comprar online

farmacias online seguras en espaГ±a: Cialis generico – farmacia online envГo gratis

http://tadalafilo.bid/# farmacia online envГo gratis

farmacias direct

http://sildenafilo.men/# comprar viagra en espaГ±a amazon

farmacias direct: comprar cialis online seguro opiniones – farmacia online espaГ±a envГo internacional

farmacias online seguras en espaГ±a: tadalafilo – farmacia online espaГ±a envГo internacional

farmacia online madrid: farmacia online envio gratis – farmacias online seguras

http://sildenafilo.men/# venta de viagra a domicilio

п»їfarmacia online espaГ±a

viagra 50 mg prezzo in farmacia pillole per erezione immediata viagra originale recensioni

farmacia online: Cialis generico farmacia – top farmacia online

cialis farmacia senza ricetta viagra farmacia esiste il viagra generico in farmacia

migliori farmacie online 2024: Cialis generico controindicazioni – migliori farmacie online 2024

http://tadalafilit.com/# Farmacie on line spedizione gratuita

top farmacia online

acquisto farmaci con ricetta acquisto farmaci con ricetta Farmacia online miglior prezzo

migliori farmacie online 2024: Farmacie online sicure – Farmacie online sicure

viagra naturale in farmacia senza ricetta: viagra prezzo – pillole per erezione immediata

farmacia online senza ricetta farmacia online migliore comprare farmaci online all’estero

viagra generico recensioni: viagra prezzo – viagra naturale

farmacie online autorizzate elenco Cialis generico controindicazioni farmacia online senza ricetta

http://farmaciait.men/# migliori farmacie online 2024

top farmacia online

migliori farmacie online 2024: Cialis generico 20 mg 8 compresse prezzo – top farmacia online

farmacie online affidabili Farmacia online piu conveniente farmaci senza ricetta elenco

acquisto farmaci con ricetta Brufen 600 senza ricetta farmacie online autorizzate elenco

alternativa al viagra senza ricetta in farmacia: viagra generico – pillole per erezioni fortissime

Farmacie on line spedizione gratuita: Ibuprofene 600 generico prezzo – Farmacie online sicure

https://farmaciait.men/# top farmacia online

farmacie online sicure

comprare farmaci online all’estero Tadalafil generico migliore farmacia online piГ№ conveniente

Farmacia online miglior prezzo Farmacie che vendono Cialis senza ricetta comprare farmaci online con ricetta

farmacie online sicure: Cialis generico farmacia – Farmacia online miglior prezzo

farmacie online sicure Ibuprofene 600 generico prezzo migliori farmacie online 2024

http://tadalafilit.com/# п»їFarmacia online migliore

farmacie online autorizzate elenco

miglior sito per comprare viagra online viagra generico viagra 100 mg prezzo in farmacia

siti sicuri per comprare viagra online: viagra farmacia – kamagra senza ricetta in farmacia

Farmacie online sicure Cialis generico 5 mg prezzo farmaci senza ricetta elenco

migliori farmacie online 2024 top farmacia online farmacia online senza ricetta

http://brufen.pro/# BRUFEN 600 prezzo in farmacia

migliori farmacie online 2024

farmacia online senza ricetta: Cialis generico farmacia – farmacia online senza ricetta

farmaci senza ricetta elenco Cialis generico 20 mg 8 compresse prezzo farmaci senza ricetta elenco

top farmacia online: Farmacie che vendono Cialis senza ricetta – comprare farmaci online all’estero

farmacia online senza ricetta Cialis generico 20 mg 8 compresse prezzo comprare farmaci online con ricetta

http://farmaciait.men/# farmacie online affidabili

farmacie online sicure

farmacia online: Cialis generico controindicazioni – Farmacia online miglior prezzo

farmacia online farmacia online senza ricetta farmacie online affidabili

cialis farmacia senza ricetta viagra generico kamagra senza ricetta in farmacia

farmacie online sicure: Brufen antinfiammatorio – Farmacie online sicure

http://ventolininhaler.pro/# purchase ventolin inhaler online

rybelsus rybelsus price cheap Rybelsus 14 mg

buy lasix online: furosemide online – lasix medication

lasix for sale: cheap lasix – lasix generic

buying neurontin online: neurontin 300 mg caps – neurontin 800 mg

https://furosemide.men/# furosemida

cost of prednisone 5mg tablets can you buy prednisone over the counter prednisone over the counter australia

rybelsus price: Semaglutide pharmacy price – buy semaglutide online

lasix 100 mg: cheap lasix – lasix online

prednisone 4mg: mail order prednisone – prednisone 2.5 mg tab

furosemida: buy furosemide – lasix 100 mg

https://gabapentin.site/# prescription medication neurontin

buy rybelsus: cheap Rybelsus 14 mg – rybelsus cost

neurontin prescription medication: neurontin pills – medicine neurontin capsules

neurontin 400 mg cost: neurontin oral – neurontin discount

https://furosemide.men/# furosemide 100mg

prednisone uk buy: prednisone 50 mg price – prednisone 10mg tabs

buy ventolin over the counter with paypal: buy albuterol inhaler – ventolin price uk

reputable indian pharmacies Indian pharmacy international shipping reputable indian online pharmacy

best online pharmacy india: п»їlegitimate online pharmacies india – reputable indian online pharmacy

buying prescription drugs in mexico: mexico drug stores pharmacies – mexican pharmaceuticals online

https://canadapharma.shop/# cheap canadian pharmacy

best online pharmacies in mexico: mexican online pharmacies prescription drugs – reputable mexican pharmacies online

http://mexicanpharma.icu/# reputable mexican pharmacies online

indian pharmacy paypal Indian pharmacy international shipping best online pharmacy india

reputable canadian online pharmacies: Online medication home delivery – safe canadian pharmacy

http://canadapharma.shop/# canadian pharmacy price checker

world pharmacy india: indian pharmacy – india pharmacy

mexico drug stores pharmacies medication from mexico best online pharmacies in mexico

https://mexicanpharma.icu/# best online pharmacies in mexico

pharmacies in canada that ship to the us: Pharmacies in Canada that ship to the US – canadapharmacyonline legit

buying from online mexican pharmacy https://mexicanpharma.icu/# mexican online pharmacies prescription drugs

buying from online mexican pharmacy

https://canadapharma.shop/# real canadian pharmacy

mexico drug stores pharmacies buying prescription drugs in mexico pharmacies in mexico that ship to usa

http://canadapharma.shop/# canadian pharmacies compare

Exceptional post however , I was wanting to know if you could write a litte more on this subject? I’d be very grateful if you could elaborate a little bit more. Thank you!

mexican mail order pharmacies mexican pharma mexico drug stores pharmacies

http://indiadrugs.pro/# indian pharmacy online

vente de mГ©dicament en ligne: pharmacie en ligne pas cher – pharmacie en ligne france livraison belgique

mexican online pharmacies prescription drugs: mexican pharma – mexican border pharmacies shipping to usa

purple pharmacy mexico price list

https://clssansordonnance.icu/# pharmacie en ligne france livraison belgique

acheter mГ©dicament en ligne sans ordonnance pharmacie en ligne sans ordonnance pharmacie en ligne france fiable

Achat mГ©dicament en ligne fiable: Cialis sans ordonnance pas cher – pharmacie en ligne sans ordonnance

pharmacie en ligne france livraison internationale: cialis sans ordonnance – vente de mГ©dicament en ligne

You are a very bright person!

http://clssansordonnance.icu/# pharmacie en ligne fiable

pharmacie en ligne pas cher cialis prix vente de mГ©dicament en ligne

acheter mГ©dicament en ligne sans ordonnance: Pharmacies en ligne certifiees – pharmacie en ligne fiable

п»їpharmacie en ligne france: pharmacie en ligne – Pharmacie en ligne livraison Europe

pharmacie en ligne fiable Cialis generique achat en ligne pharmacies en ligne certifiГ©es

Viagra sans ordonnance 24h suisse: Viagra generique en pharmacie – Viagra gГ©nГ©rique sans ordonnance en pharmacie

pharmacie en ligne fiable: Pharmacie sans ordonnance – vente de mГ©dicament en ligne

https://pharmaciepascher.pro/# Pharmacie Internationale en ligne

Viagra pas cher livraison rapide france viagra en ligne Viagra en france livraison rapide

Viagra pas cher paris: Viagra generique en pharmacie – Le gГ©nГ©rique de Viagra

What’s Going down i’m new to this, I stumbled upon this I have found It positively helpful and it has aided me out loads. I am hoping to contribute & aid other users like its helped me. Great job.

https://ozempic.art/# ozempic

buy rybelsus online: semaglutide tablets – semaglutide online

semaglutide cost: buy rybelsus online – semaglutide online

https://ozempic.art/# buy cheap ozempic

https://rybelsus.shop/# semaglutide cost

buy semaglutide online: rybelsus cost – semaglutide tablets

rybelsus pill: rybelsus cost – semaglutide tablets

https://rybelsus.shop/# semaglutide cost

https://rybelsus.shop/# semaglutide online

semaglutide cost: buy rybelsus online – cheapest rybelsus pills

semaglutide cost rybelsus coupon buy semaglutide online

rybelsus price: semaglutide cost – rybelsus cost

https://ozempic.art/# ozempic generic

buy ozempic pills online: buy ozempic pills online – Ozempic without insurance

https://rybelsus.shop/# semaglutide cost

semaglutide online: buy semaglutide online – semaglutide cost

http://ozempic.art/# Ozempic without insurance

rybelsus pill: cheapest rybelsus pills – rybelsus coupon

buy ozempic pills online ozempic generic buy ozempic

ozempic coupon: Ozempic without insurance – ozempic online

https://ozempic.art/# buy cheap ozempic

rybelsus pill buy semaglutide pills buy semaglutide pills

semaglutide cost: semaglutide cost – rybelsus cost

https://ozempic.art/# Ozempic without insurance

ozempic coupon: ozempic online – buy cheap ozempic

rybelsus cost: rybelsus coupon – buy semaglutide online

https://rybelsus.shop/# rybelsus coupon

buy semaglutide pills: buy semaglutide online – semaglutide online

ozempic online: Ozempic without insurance – buy cheap ozempic

rybelsus coupon buy semaglutide online rybelsus cost

https://ozempic.art/# ozempic coupon

https://ozempic.art/# Ozempic without insurance

semaglutide online: buy rybelsus online – cheapest rybelsus pills

buy ozempic pills online ozempic coupon ozempic coupon

https://ozempic.art/# buy ozempic pills online

ozempic generic: buy ozempic pills online – ozempic

http://ozempic.art/# ozempic

cheapest rybelsus pills buy rybelsus online cheapest rybelsus pills

https://ozempic.art/# ozempic

rybelsus pill: buy semaglutide online – semaglutide tablets

https://ozempic.art/# ozempic cost

https://rybelsus.shop/# semaglutide cost

Ozempic without insurance ozempic buy ozempic

pin up azerbaijan: pin up azerbaijan – pin-up casino giris

pin-up casino: pin up guncel giris – pin up aviator

pin up guncel giris pin-up casino giris pin-up casino giris

https://pinupkz.tech/# пин ап казахстан

pin-up casino: pin up guncel giris – pin up guncel giris

pin up bet: pin up aviator – pin up

pin up casino: pin up – pin up 306

pin up казино https://pinupkz.tech/# пин ап казино вход

pin up

пин ап казино онлайн: пинап кз – пин ап

pin up казино: пин ап казино вход – pin up

pin up зеркало пин ап зеркало пин ап

пинап казино https://pinupkz.tech/# пинап кз

pin up казино

pin up az: pin up az – pin up casino

pin up azerbaijan: pinup azerbaycan – pin-up oyunu

pin up casino giris pin up casino guncel giris pin up giris

pin up http://pinupturkey.pro/# pin up

pin up казино

pin up зеркало: пин ап казино вход – пин ап вход

пин ап казино http://pinupturkey.pro/# pin-up casino giris

пин ап казино онлайн

https://pinupturkey.pro/# pin up casino

пинап кз: пин ап кз – pin up kz

пин ап казино онлайн: пинап кз – пин ап казино

pin up pin up зеркало пин ап официальный сайт

pin up казино https://pinupru.site/# пин ап вход

пин ап казино

pin-up casino giris: pinup azerbaycan – pin-up casino giris

https://pinupkz.tech/# pin up

pin up pin up guncel giris pin up

пин ап казино вход https://pinupru.site/# pin up зеркало

pin up kz

пин ап кз: пинап казино – пин ап кз

minocycline 50 mg tablet stromectol ivermectin buy minocycline warnings

https://zithromax.company/# zithromax capsules australia

https://amoxil.llc/# order amoxicillin no prescription

rybelsus cost buy semaglutide online rybelsus cost

buy amoxicillin online without prescription: buy amoxil – amoxicillin 500 mg without a prescription

http://zithromax.company/# where can i purchase zithromax online

https://gabapentin.auction/# price of neurontin

https://semaglutide.win/# Buy semaglutide pills

can i buy zithromax online

https://amoxil.llc/# amoxicillin without a prescription

generic neurontin pill neurontin canada online neurontin price in india

buy amoxicillin online cheap: cheapest amoxil – where to buy amoxicillin over the counter

https://stromectol.agency/# minocycline 100 mg over the counter

https://semaglutide.win/# semaglutide

zithromax online no prescription

neurontin 204 cheapest gabapentin neurontin

http://semaglutide.win/# Buy semaglutide pills

https://semaglutide.win/# Rybelsus 14 mg price

https://gabapentin.auction/# generic neurontin cost

generic zithromax 500mg india

zithromax tablets for sale generic zithromax zithromax 1000 mg online

https://zithromax.company/# zithromax 250

neurontin 600 mg price: gabapentin best price – neurontin 300 mg cap

https://gabapentin.auction/# generic neurontin pill

amoxicillin 500mg prescription cheapest amoxil amoxicillin 500mg capsules uk

https://stromectol.agency/# cost of ivermectin

buy zithromax canada

https://gabapentin.auction/# 2000 mg neurontin

Those are yours alright! . We at least need to get these people stealing images to start blogging! They probably just did a image search and grabbed them. They look good though!

Rybelsus 14 mg price: rybelsus price – Rybelsus 14 mg price

https://stromectol.agency/# minocycline for rheumatoid arthritis

Excellent website. Plenty of useful info here. I am sending it to several friends ans also sharing in delicious. And obviously, thanks for your effort!

neurontin price gabapentin best price neurontin oral

https://zithromax.company/# average cost of generic zithromax

https://gabapentin.auction/# neurontin 600

zithromax

Rybelsus 14 mg: cheap Rybelsus 14 mg – buy rybelsus

https://stromectol.agency/# minocycline drug

amoxicillin buy canada Amoxicillin For sale can i buy amoxicillin over the counter

https://semaglutide.win/# buy semaglutide online

buy zithromax 1000mg online

http://stromectol.agency/# minocycline 100mg pills

https://stromectol.agency/# ivermectin purchase

neurontin tablets no script: gabapentin price – neurontin 800mg

purchase neurontin online gabapentin for sale neurontin canada

https://gabapentin.auction/# neurontin 100 mg

how to buy zithromax online

zithromax capsules price zithromax over the counter zithromax 500 mg lowest price online

http://semaglutide.win/# Rybelsus 7mg

where can i get zithromax over the counter

medicine amoxicillin 500mg buy amoxil amoxil generic

https://amoxil.llc/# over the counter amoxicillin

buy generic zithromax online

https://gabapentin.auction/# prescription medication neurontin

cost of neurontin 100mg: neurontin 300 mg price in india – neurontin cap 300mg

stromectol tablets cheapest stromectol stromectol price us

https://amoxil.llc/# amoxicillin 500mg price in canada

http://amoxil.llc/# can you purchase amoxicillin online

where can i buy zithromax uk

Buy compounded semaglutide online: semaglutide – semaglutide

neurontin cost in singapore order gabapentin neurontin 600 mg coupon

https://gabapentin.auction/# gabapentin generic

can ed be cured http://indianpharmdelivery.com/# Online medicine order

http://mexicanpharm24.pro/# mexican drugstore online

indian pharmacy paypal

reputable mexican pharmacies online: pharmacies in mexico that ship to usa – mexico drug stores pharmacies

Sharing is caring the say, and you’ve done a fantastic job in sharing your knowledge on your blog. It would be great if you check out my page, too, at QH7 about Car Purchase.

mexico drug stores pharmacies mexican mail order pharmacies mexican online pharmacies prescription drugs

mexico drug stores pharmacies: mexico drug stores pharmacies – mexico drug stores pharmacies

causes for ed https://indianpharmdelivery.com/# indian pharmacies safe

This web site is mostly a stroll-by way of for the entire information you wished about this and didn’t know who to ask. Glimpse here, and also you’ll definitely uncover it.

Online medicine order: Online medicine home delivery – reputable indian pharmacies

http://drugs24.pro/# online medications

online pharmacy india

pharmacies in mexico that ship to usa buying prescription drugs in mexico mexican mail order pharmacies

buying prescription drugs in mexico online: mexican drugstore online – mexican rx online

best male enhancement: male erection pills – drugs for ed

natural cure for ed buy canadian drugs homepage

https://mexicanpharm24.pro/# mexican rx online

п»їlegitimate online pharmacies india

online pharmacy india: cheapest online pharmacy india – online shopping pharmacy india

mexican online pharmacies prescription drugs: buying from online mexican pharmacy – reputable mexican pharmacies online

best erection pills http://indianpharmdelivery.com/# india pharmacy mail order

medicine in mexico pharmacies mexican pharmaceuticals online mexican drugstore online

buying prescription drugs in mexico online: mexican pharmaceuticals online – buying prescription drugs in mexico

online pharmacy india: indianpharmacy com – top online pharmacy india

https://drugs24.pro/# vacuum pumps for ed

buy medicines online in india

medication from mexico pharmacy buying prescription drugs in mexico mexican drugstore online

ed online pharmacy http://mexicanpharm24.pro/# buying prescription drugs in mexico online

ed drugs list: sildenafil without a doctor’s prescription – ed products

medicine in mexico pharmacies mexican pharmaceuticals online pharmacies in mexico that ship to usa

https://drugs24.pro/# the best ed pill

top 10 pharmacies in india

non prescription ed drugs https://mexicanpharm24.pro/# pharmacies in mexico that ship to usa

levitra without a doctor prescription erection pills muse for ed

best drugs for erectile dysfunction http://mexicanpharm24.pro/# buying prescription drugs in mexico online

https://mexicanpharm24.pro/# best online pharmacies in mexico

reputable indian online pharmacy

best india pharmacy world pharmacy india pharmacy website india

cheap plavix antiplatelet drug: clopidogrel pro – buy Clopidogrel over the counter

http://paxlovid1st.shop/# paxlovid buy

erectile dysfunction natural remedies

buy Clopidogrel over the counter: clopidogrel pills – Cost of Plavix without insurance

https://stromectol1st.shop/# ivermectin 3 mg dose

ed cures that work

buy Clopidogrel over the counter: here – buy plavix

https://stromectol1st.shop/# minocycline 50 mg without a doctor

buy prescription drugs from india

purchase oral ivermectin stromectol 1st shop ivermectin for sale

https://stromectol1st.shop/# ivermectin 1 cream

natural drugs for ed

stromectol order: stromectol 1st – minocycline foam

paxlovid pharmacy: paxlovid shop – paxlovid buy

ivermectin 5 mg stromectol fast delivery ivermectin 0.5%

http://stromectol1st.shop/# ivermectin 6mg tablet for lice

reputable indian pharmacies

https://stromectol1st.shop/# stromectol prices

impotence pills

rybelsus cost: rybelsus – rybelsus.icu

stromectol pills stromectol 1st minocycline 100 mg over the counter

ivermectin human: minocycline hydrochloride – minocycline capsulas

http://paxlovid1st.shop/# paxlovid india

how to cure ed

Plavix 75 mg price: check clopidogrel pro – plavix best price

https://stromectol1st.shop/# minocycline 100mg pills

india pharmacy mail order

rybelsus.icu cheaper Buy semaglutide

rybelsus.icu: cheaper – buy rybelsus

http://paxlovid1st.shop/# paxlovid covid

ed pumps

buy semaglutide online: buy semaglutide online – buy rybelsus

ivermectin 20 mg: stromectol fast delivery – minocycline hydrochloride

paxlovid pharmacy paxlovid shop Paxlovid buy online

http://stromectol1st.shop/# buy stromectol

online pharmacy india

https://rybelsus.icu/# buy rybelsus

solutions for ed

ivermectin cream uk: best price shop – minocycline 50 mg tablets for humans for sale

Buy semaglutide: good price – rybelsus cost

rybelsus generic buy rybelsus rybelsus

http://paxlovid1st.shop/# paxlovid covid

ed pills online

http://stromectol1st.shop/# minocycline 50 mg tablets

cheapest online pharmacy india

paxlovid india: best price on pills – paxlovid pharmacy

paxlovid cost without insurance: shop – paxlovid generic

paxlovid cost without insurance buy here paxlovid india

http://stromectol1st.shop/# ivermectin cream uk

cure ed

paxlovid pill: buy here – paxlovid pharmacy

good price Buy semaglutide Semaglutide pharmacy price

Plavix 75 mg price: here – п»їplavix generic

https://stromectol1st.shop/# buy minocycline 100 mg

indianpharmacy com

cheaper: rybelsus – Buy semaglutide

Clopidogrel 75 MG price clopidogrel pro cheap plavix antiplatelet drug

rybelsus price: cheaper – rybelsus price

I’m still learning from you, but I’m making my way to the top as well. I definitely love reading everything that is written on your blog.Keep the posts coming. I loved it!

https://stromectol1st.shop/# ivermectin price usa

reputable indian pharmacies

buy clopidogrel bisulfate: plavix price – generic plavix

is minocycline an antibiotic stromectol fast delivery cost of ivermectin

ivermectin 1: stromectol shop – generic stromectol

пин ап: пин ап официальный сайт – пин ап зеркало

canl? casino siteleri slot casino siteleri dunyan?n en iyi casino siteleri

1хбет: 1xbet скачать – 1xbet

1xbet скачать: 1xbet – 1xbet официальный сайт

pinup az: pin up azerbaycan – pin up azerbaycan

canl? casino canl? casino siteleri dunyan?n en iyi casino siteleri

http://1winrussia.online/# 1хставка

пинап казино

canl? casino: casino oyunlar? – casino sitesi

pin up 306: pin up azerbaycan – pin up azerbaycan

пинап кз: пинап – пинап

pin-up: pinup az – pin up

https://1winci.icu/# пин ап зеркало

пин ап казино вход

пин ап: пинап кз – пин ап

пинап казино пин ап казино вход пинап

пин ап официальный сайт: пин ап вход – пин ап зеркало

pin up casino: pin up 306 – pin up

пин ап вход: пин ап вход – пинап зеркало

https://1winrussia.online/# 1xbet зеркало

пинап казино

пин ап казино вход: пин ап кз – пин ап казино вход

пинап зеркало: пин ап зеркало – пин ап официальный сайт

casino oyunlar?: casino siteleri – canl? casino

1xbet официальный сайт 1хставка 1хбет

https://1wintr.fun/# canl? casino siteleri

пин ап казино вход

пин ап казино: пинап казино – пинап кз

1xbet зеркало: 1xbet официальный сайт – 1хставка

dunyan?n en iyi casino siteleri: en iyi casino siteleri – cazino

1хбет: 1xbet – 1xbet

https://1wintr.fun/# casino siteleri

пин ап казино

en iyi casino siteleri casino siteleri canl? casino siteleri

casino siteleri: h?zl? casino – slot casino siteleri

1xbet скачать: 1xbet – 1xbet официальный сайт

1xbet официальный сайт: 1xbet скачать – 1xbet официальный сайт

https://1winci.icu/# пин ап зеркало

пин ап казино вход

пинап: пин ап казино вход – пинап кз

пин ап вход пинап зеркало пин ап вход

пин ап зеркало: пинап зеркало – пин ап

https://1winindia.tech/# пинап кз

пин ап кз

пин ап казино: пин ап – пин ап кз

pin up: pin-up casino giris – pin up casino

1xbet скачать 1xbet зеркало 1хбет

ed pills for sale: foods for ed – how to treat ed

indian pharmacies safe: indian pharmacy paypal – pharmacy website india

http://drugs1st.store/# male enhancement products

website: ed symptoms – medications online

mexico drug stores pharmacies buying prescription drugs in mexico mexican border pharmacies shipping to usa

buying prescription drugs in mexico: mexico drug stores pharmacies – pharmacies in mexico that ship to usa

http://indianpharm1st.com/# india pharmacy

doctors for erectile dysfunction: prescription drugs online – pharmacy medications

cheapest online pharmacy india: indian pharmacies safe – reputable indian online pharmacy

best online pharmacy india: online shopping pharmacy india – Online medicine order

http://drugs1st.store/# ed pharmacy

medication from mexico pharmacy mexican drugstore online mexican border pharmacies shipping to usa

indian pharmacy online: indian pharmacy paypal – india online pharmacy

http://indianpharm1st.com/# top 10 online pharmacy in india

pharmacies in mexico that ship to usa: reputable mexican pharmacies online – reputable mexican pharmacies online

pharmacy website india: online pharmacy india – п»їlegitimate online pharmacies india

erection pills online erectile dysfunction treatment ed pills that really work

https://indianpharm1st.com/# top 10 pharmacies in india

supplements for ed: best ed medications – best ed pills that work

reputable indian online pharmacy: top online pharmacy india – top 10 online pharmacy in india

indian pharmacy paypal: india pharmacy mail order – indian pharmacy

https://indianpharm1st.com/# reputable indian online pharmacy

sweet bonanza: sweet bonanza – sweet bonanza nas?l oynan?r

https://pinup-az.bid/# pin up

http://biznes-fabrika.kz/# пин ап 634

pin up win

pin up kz Пин Ап Казино Официальный Сайт пин ап кз

sweet bonanza oyna: sweetbonanzatrpro – sweetbonanzatr.pro

http://pinup-az.bid/# pin up azerbaycan

pin up win

https://biznes-fabrika.kz/# Пин Ап Казино Официальный Сайт

пин ап казино онлайн: Пин Ап Казахстан – пин ап кз

пин ап: Пин Ап Казино Официальный Сайт в России – пин ап вход

http://pinup-az.bid/# pinup

pin up zerkalo

pinco пин ап казино пинап казино

Официальный Сайт: pin up zerkalo – пин ап зеркало

https://sweetbonanzatr.pro/# sweetbonanzatrpro

sweet bonanza: sweet bonanza – sweet bonanza

пин ап зеркало: пин ап вход – пинко

https://sweetbonanzatr.pro/# sweet bonanza

pinup bet and casino

pinco пинко пин ап

pin up zerkalo: pin up zerkalo – Пин Ап Казино Официальный Сайт в России

pin up azerbaycan: pinup az – pin up casino

http://biznes-fabrika.kz/# пин ап 634

https://pinupzerkalo.fun/# pinco

pin up casino

sweet bonanza: sweet bonanza – sweetbonanzatr.pro

pin-up: pinup – pin up azerbaycan

sweet bonanza nas?l oynan?r sweet bonanza sweet bonanza

https://sweetbonanzatr.pro/# sweetbonanzatr.pro

pinup bet and casino

пин ап: пин ап вход – пин ап казино

https://biznes-fabrika.kz/# Пин Ап Казино Официальный Сайт

пин ап казино: pin up zerkalo – Пин Ап Казино Официальный Сайт в России

sweet bonanza: sweet bonanza tr – sweet bonanza

http://pinupzerkalo.fun/# пин ап

pin up casino

пин ап казино пинап казино пинап казино

pinco: Официальный Сайт – pinco

sweet bonanza: sweetbonanzatr.pro – sweet bonanza

http://biznes-fabrika.kz/# pin up kz

buy gabapentin: same-day delivery – Neurontin online

Specialists: semaglutide online – Specialists

http://gabapentin1st.pro/# gabapentin best price

https://gabapentin1st.pro/# same-day delivery

stromectol delivery usa: cheapest – stromectol online

Care provides: licensed gabapentin – Care provides

https://semaglutide.ink/# semaglutide online

good price: stromectol best price – good price

shop: amoxil 1st shop – top-rated pills

cheap: amoxil price – amoxil price

https://amoxil1st.shop/# amoxil online

https://gabapentin1st.pro/# Care provides

stromectol online: stromectol store – find bets price

top-rated pills: amoxil 1st shop – shop

erectile dysfunction medication low cost pharmacy drugs to treat ed

mexico drug stores pharmacies: mexican drugs – mexico pharmacies prescription drugs

male ed drugs http://indianpharm24.pro/# best online pharmacy india

top online pharmacy india India pharmacy delivery indian pharmacy

http://mexicanpharm24.cheap/# mexico pharmacies prescription drugs

natural ed pills

mail order pharmacy india: indian pharm 24 – Online medicine order

non prescription erection pills cheap prescription drugs ed clinics

best online pharmacies in mexico: Legit online Mexican pharmacy – mexico drug stores pharmacies

dysfunction erectile https://mexicanpharm24.cheap/# pharmacies in mexico that ship to usa

mexico drug stores pharmacies mexico pharmacy cheap purple pharmacy mexico price list

https://pharm24.pro/# ed meds

ed drugs compared

mexican pharmaceuticals online: mexico pharmacy – mexican rx online

canadian drugs cheaper medications best ed treatments

male ed http://mexicanpharm24.cheap/# mexico drug stores pharmacies

best india pharmacy: Indian pharmacy online – reputable indian online pharmacy

https://pharm24.pro/# foods for ed

soma therapy ed

generic ed pills cheap pharmacy over the counter ed medication

Hey there, You have done an excellent job. I’ll certainly digg it and personally suggest to my friends. I am sure they will be benefited from this web site.

medicine in mexico pharmacies: mexico pharmacy – medicine in mexico pharmacies

buy prescription drugs without doctor https://indianpharm24.pro/# world pharmacy india

buying prescription drugs in mexico online mexican pharmacy pharmacies in mexico that ship to usa

mexico pharmacies prescription drugs: Legit online Mexican pharmacy – pharmacies in mexico that ship to usa

http://mexicanpharm24.cheap/# mexico drug stores pharmacies

best ed solution

errectile disfunction cheap prescription drugs ed for men

ed symptoms: cheap drugs online – ed supplements

viagra without a doctor prescription http://indianpharm24.pro/# india pharmacy mail order

erectile dysfunction treatment cheap pharmacy online natural ed pills

https://pharm24.pro/# the best ed pill

erection pills

best ed medicine cheap drugs how to overcome ed naturally

top 10 online pharmacy in india: Indian pharmacy worldwide delivery – pharmacy website india

prescription meds without the prescriptions https://pharm24.pro/# ed trial pack

mexican rx online: mexico pharmacy – purple pharmacy mexico price list

http://pharm24.pro/# best erection pills

buy ed pills online

cialis without doctor prescription http://mexicanpharm24.cheap/# medication from mexico pharmacy

top online pharmacy india: Indian pharmacy international shipping – reputable indian online pharmacy

prescription drugs online without: cheap prescription drugs – natural help for ed

https://indianpharm24.pro/# Online medicine home delivery

canadian drug

amoxicillin without a doctor’s prescription http://mexicanpharm24.cheap/# buying prescription drugs in mexico

matadorbet matadorbet.bid matadorbet

ultrabet tr online: ultrabet yeni giris 1125 – ultrabet guncel

deneme bonusu veren yeni siteler https://casinositeleri.win/# guvenilir casino siteleri

http://slot-tr.online/# slot siteleri

deneme bonusu veren siteler yeni

Casino Siteleri: guvenilir casino siteleri – casino siteleri win

ultrabet tr online ultrabet guncel ultrabet

Casino Siteleri: Casino Siteleri – Casino Siteleri

Deneme Bonusu Veren Siteler Deneme Bonusu Veren Siteler casino siteleri win

ultrabet: ultrabet giris – ultrabet bonus

deneme bonusu veren siteler yeni https://denemebonusuverensiteler.top/# deneme bonusu veren siteler 2024

deneme bonusu veren siteler yerliarama.org: deneme bonusu veren siteler 2024 – deneme bonusu veren siteler yerliarama.org

https://slot-tr.online/# slot siteleri

deneme bonusu veren siteler

slot oyunlar? az parayla cok kazandiran slot oyunlar? slot oyunlar? puf noktalar?

matadorbet.bid: matadorbet giris – matadorbet bid

ultrabet guncel: ultrabet giris – ultrabet tr online

deneme bonusu veren yeni siteler deneme bonusu veren siteler mycbet.com deneme bonusu veren siteler yerliarama.org

deneme bonusu veren siteler yerliarama.org https://slot-tr.online/# slot tr online

az parayla cok kazandiran slot oyunlar?: slot oyunlar? – en kazancl? slot oyunlar?

ultrabet bonus ultrabet yeni giris 1125 ultrabet bonus

ultrabet: ultrabet tr online – ultrabet guncel

slot oyunlar? puf noktalar?: slot oyunlar? puf noktalar? – slot oyunlar?

denemebonusuverensiteler.top deneme bonusu veren siteler mycbet.com deneme bonusu veren siteler yerliarama.org

Casino Siteleri: Casino Siteleri – Casino Siteleri

Casino Siteleri: guvenilir casino siteleri – Casino Siteleri

matadorbet giris matadorbet bid matadorbet giris

buy lasix fur pharm: furosemide furpharm.com – buy furosemide online

best ed pills online cheapest ed pills ere pharm erepharm.com

http://kampharm.shop/# kamagra

http://furpharm.com/# furosemide furpharm.com

kam pharm shop: kampharm shop – Kam Pharm

kamagra oral jelly Kam Pharm buy kamagra oral jelly Kam Pharm

https://furpharm.com/# furosemide furpharm.com

ed pills: ED meds online – ere pharm

lasix furpharm lasix

https://gabapharm.com/# buy gabapentin online

https://erepharm.com/# erepharm pills

buy kamagra oral jelly Kam Pharm: Kamagra Kam Pharm – Kam Pharm

fur pharm cheapest lasix furosemide furpharm.com

https://erepharm.com/# ed pills

https://rybpharm.com/# buy rybelsus rybpharm

kampharm.shop: kam pharm shop – buy kamagra oral jelly Kam Pharm

ED meds online ed pills erepharm pills